# SIEMENS Preliminary IC-SPECIFICATION TDA 6060XS, TDA 6060G

## **Multistandard Modulator / PLL**

|                                     | <u>page</u> |

|-------------------------------------|-------------|

| Contents                            | 1           |

| Functional Description, Application | 2           |

| Pin Definition and Function         | 3           |

| Block Diagram                       | 4           |

| Circuit Description                 | 5-10        |

| Pinning, Package                    | 11          |

| Absolute Maximum Ratings            | 12          |

| Operational Range                   | 13          |

| AC/DC Characteristics               | 14-18       |

| Test Procedures                     | 19          |

| Equivalent I/O-Schematics           | 20-24       |

| I <sup>2</sup> C-Bus Timing         | 25          |

| Test Circuit Diagram                | 26          |

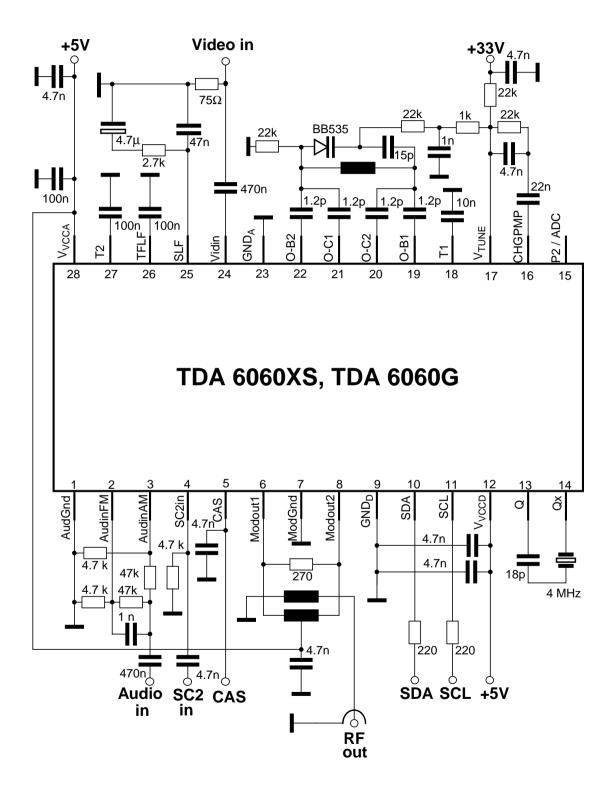

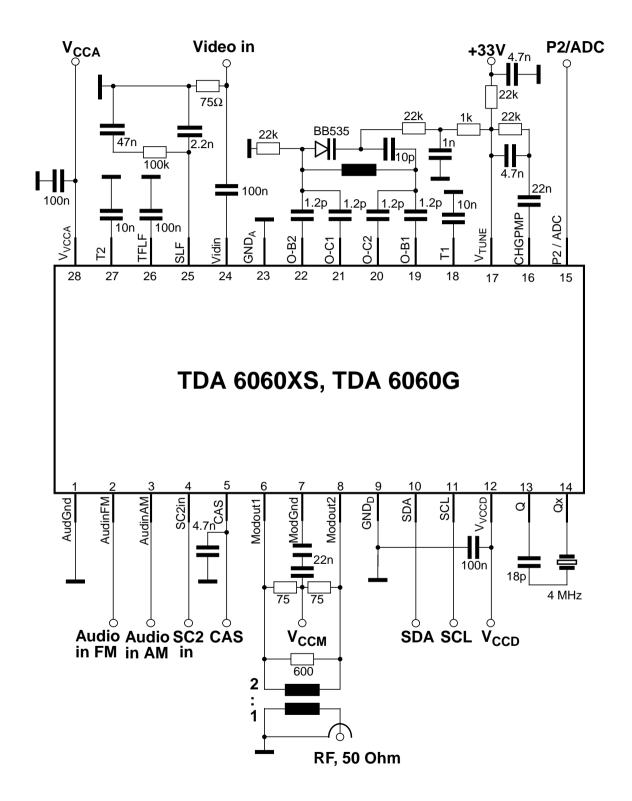

| Application Board Circuit Diagram   | 27          |

#### **Functional Description, Application**

#### Multistandard Modulator / PLL

#### **Functional Description**

The TDA 6060XS device combines a digitally programmable phase locked loop (PLL), with a multistandard video modulator and a programmable sound FM and AM modulator.

The PLL block with four hard-switched chip addresses forms a digitally programmable phase locked loop. With a 4 MHz quartz crystal, the PLL permits precise setting of the frequency of the modulator oscillator from 30 MHz to 950 MHz in increments of 250 kHz. The tuning process is controlled by a microprocessor via an I<sup>2</sup>C bus. The device has one output port, which can also be used as an A/D converter input. A flag is set when the loop is locked. The lock flag can be read by the processor via the I<sup>2</sup>C bus.

The modulator block includes a clamped video input amplifier followed by a double balanced mixer as a RF modulator, a frequency and amplitude-stable balanced oscillator for the VHF, Hyper band and the UHF range (with different tank circuits), a digitally programmable sound FM / AM modulator, a second audio carrier input and a low-noise reference voltage source.

#### **Features**

- Frequency and amplitude-stable balanced oscillator for the VHF, Hyper band and the UHF frequency range

- Clamped video input with peak white level detection for I<sup>2</sup>C bus controlled gain setting of the video amplifier

- Programmable sound carriers 4.5 MHz, 5.5 MHz, 6 MHz, 6.5 MHz

- Second sound carrier input

- Balanced RF output

- Low-noise reference voltage

- 1-chip system for μC control (I<sup>2</sup>C bus)

- Fast I<sup>2</sup>C bus mode possible

- 4 programmable chip addresses

- Smallest possible lock-in time; no asynchronous divider stage

- Short pull-in time for quick channel switch-over and optimized loop stability

- One high-current switch output

- 5-level A/D converter

- Lock-in flag

- Power-down flag

- Few external components

- Package TSSOP 28

- 5 V supply voltage

#### **Application**

The TDA 6060XS is suitable for all modulator boxes The TDA 6060G has modified divider ratio for applications with +125kHz RF frequency offset (e.g. 38.875MHz, N=620+2) and reduced Sound Carrier Levels.

#### **SIEMENS Preliminary IC-SPECIFICATION TDA 6060XS, TDA 6060G**

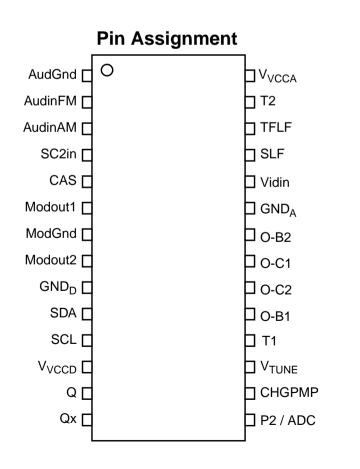

## **Pin Definitions and Functions**

#### **PLL Section**

| PIN No. | Symbol            | Function                                                                |

|---------|-------------------|-------------------------------------------------------------------------|

| 5       | CAS               | Chip address select                                                     |

| 9       | GND <sub>D</sub>  | Ground for digital block (PLL)                                          |

| 10      | SDA               | Data input/output for the I <sup>2</sup> C bus                          |

| 11      | SCL               | Clock input for the I <sup>2</sup> C bus                                |

| 12      | V <sub>VCCD</sub> | Positive supply voltage for digital block (PLL)                         |

| 13      | Q                 | 4 MHz low-impedance crystal oscillator input                            |

| 14      | Qx                | 4 MHz low-impedance crystal oscillator input; external oscillator input |

| 15      | P2 / ADC          | Port output / ADC input                                                 |

| 16      | CHGPMP            | Charge pump output / loop filter                                        |

| 17      | V <sub>TUNE</sub> | Open collector output for pull up resistor / loop filter                |

#### **Multistandard Modulator Section**

| PIN No. | Symbol            | Function                                                                   |

|---------|-------------------|----------------------------------------------------------------------------|

| 1       | AudGnd            | Audio ground                                                               |

| 2       | AudinFM           | Audio input for FM sound IF application                                    |

| 3       | AudinAM           | Audio input for AM sound IF application                                    |

| 4       | SC2in             | Second sound carrier input                                                 |

| 6       | Modout1           | Modulator output, balanced to pin 8                                        |

| 7       | ModGnd            | Modulator output ground                                                    |

| 8       | Modout2           | Modulator output, balanced to pin 6                                        |

| 18      | T1                | Test interface input 1                                                     |

| 19      | O-B1              | Oscillator amplifier, high-impedance base input, symmetrical to O-B2       |

| 20      | O-C2              | Oscillator amplifier, high-impedance collector output, symmetrical to O-C1 |

| 21      | O-C1              | Oscillator amplifier, high-impedance collector output, symmetrical to O-C2 |

| 22      | O-B2              | Oscillator amplifier, high-impedance base input, symmetrical to O-B1       |

| 23      | GND <sub>A</sub>  | Ground for analog block                                                    |

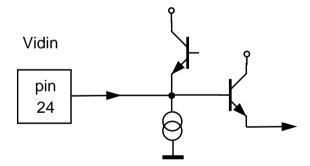

| 24      | Vidin             | Clamped video input                                                        |

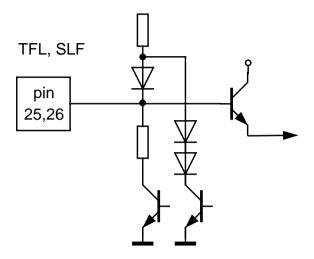

| 25      | SLF               | Sound carrier PLL loop filter                                              |

| 26      | TFLF              | Tracking filter low pass filter                                            |

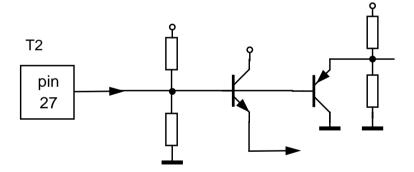

| 27      | T2                | Test interface input 2                                                     |

| 28      | V <sub>VCCA</sub> | Positive supply voltage for analog block                                   |

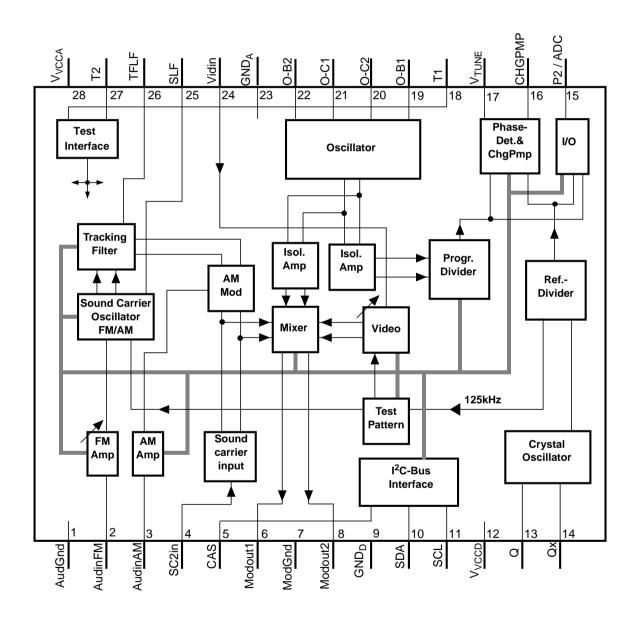

## **Block Diagram**

#### **Circuit Descripton**

#### **General Description:**

#### Modulator block

The modulator section includes a gain adjustable video amplifier, a double balanced mixer working as a AM video modulator for positive or negative modulation, a balanced oscillator for VHF, Hyper band and UHF, a sound modulator suitable for FM and AM modulation, a programmable sound carrier oscillator and a reference voltage source.

The audio signal is coupled to the gain settable audio pre-amplifier of the FM AF input (AudinFM) and to the AM input amplifier (AudinAM). The pre-emphasis is done with an external circuitry in front of the FM audio input. The FM audio amplifier allows a gain setting in four steps with the AU0 / 1 bits in the negative video modulation mode (PN = 0). The amplified audio signal is fed to the FM modulator. The modulated sound carrier is filtered by a tracked bandpass filter and added to the video signal. In the positve video modulation mode the the audio signal is directly fed to the AM sound modulator. The sound carriers are generated by a programmable on chip oscillator. The four possible frequencies are 4.5, 5.5, 6.0 and 6.5 MHz (2bit). To increase the speed of the sound PLL the loop filter current can be switched to 5I with the audio mode bits (table 4). A second FM or NICAM sound carrier may be added via the input SC2in to the internally generated carrier. The SC2in input is referenced to Audgnd and can be switched off by connecting SC2in to the supply voltage.

The positve video signal is capacitively coupled to the video input pin (Vidin). An internal clamping circuit is referenced to the sync tip level. If the video signal exceeds the maximum level the peak white level is clipped. The clipping circuit acts also as a detector and sets a flag (FLV) for the I<sup>2</sup>C bus. The video input amplifier allows a gain setting in four steps. The polarity of the video signal can be switched for positive or negative modulation. The setting to positve modulation is combined with the AM modulation of the sound carrier. For the residual carrier adjustment a sawtooth test picture is used when the video modulator is in overmodulation mode. This mode is active by conneting test pin T1 to ground.

The adjustments of the modulation depth and the picture to sound carrier ratio can be done in four steps.

The RF oscillator works as gain controlled LC tuned astable multivibrator. The output of the oscillator is decoupled by two isolation amplifiers, one for the modulator mixer and one for the synthesizer PLL. The VCO can be switched off by setting both audio mode bits to 1 in positive modulation mode (table 4) The added sound carrier and video signals are mixed with the RF oscillator signal in the double balanced mixer and then fed to both RF outputs (Modout1 / Modout2)

#### PLL and I<sup>2</sup>C bus

The oscillator signal for the RF modulator is internally DC-coupled as a differential signal at the programmable divider inputs. The signal subsequently passes through a programmable divider with ratio N = 256 through 32764 by 4 (TDA 6060G: 258 through 32766 by 4) and is then compared in a digital frequency / phase detector to a reference frequency f<sub>ref</sub> = 62.5 kHz. This frequency is derived from a balanced, low-impedance 4 MHz crystal oscillator (pin Q, Qx) or from a external signal source divided by Q = 64.

The phase detector has two outputs UP and DOWN that drive two current sources I+ and I- of a charge pump. If the negative edge of the divided VCO signal appears prior to the negative edge of the reference signal, the I+ current source pulses for the duration of the phase difference. In the reverse case the I- current source pulses. If the two signals are in phase, the charge pump output (CHGPMP) goes into the high-impedance state (PLL is locked). An active low-pass filter integrates the current pulses to generate the tuning voltage for the VCO (internal amplifier, external pullup resistor at TUNE and external RC circuitry). It should be noted, however, that the tuning voltage can alter over a long period in the high impedance state as a result of selfdischarge in the peripheral circuity. TUNE may be switched off by the control bit OS to allow external adjust-

#### **Circuit Description**

ments.

The software-switched bidirectional port P2 is a general-purpose open-collector output and can also be used as an A/D converter input.

In the internal or external 4 MHz reference oscillator mode a test pattern is generated in the reference divider. With the bit TP in the second control byte this test pattern is switched to the modulator input.

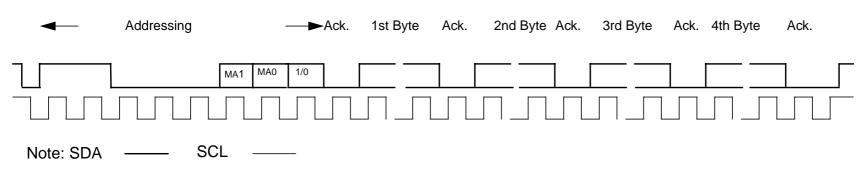

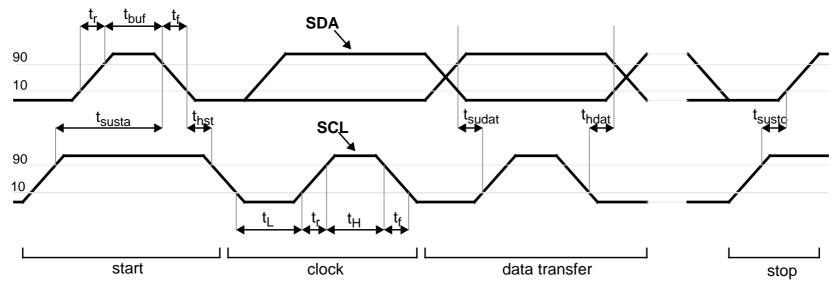

Data are exchanged between the processor and the PLL via the I<sup>2</sup>C bus. The clock is generated by the processor (input SCL), while pin SDA functions as an input or output depending on the direction of the data (open collector, external pull-up resistor). Both inputs have hysteresis and a low-pass characteristic, which enhance the noise immunity of the I<sup>2</sup>C bus.

The data from the processor pass through an I<sup>2</sup>C bus controller. Depending on their function the data are subsequently stored in registers. If the bus is free, both lines will be in the marking state (SDA, SCL are HIGH). Each telegram begins with the start condition and ends with the stop condition. Start condition: SDA goes LOW, while SCL remains HIGH. Stop condition: SDA goes HIGH while SCL remains HIGH. All further information transfer takes place during SCL = LOW, and the data is forwarded to the control logic on the positive clock edge.

The table 1 "bit allocation" should be referred to the following description. All telegrams are transmitted byteby-byte, followed by a ninth clock pulse, during which the control logic returns the SDA line to LOW (acknowledge condition). The first byte is comprised of seven address bits. These are used by the processor to select the PLL from several peripheral components (chip select). The eighth bit (R/W) determines whether data are written into (R/W = 0) or read from (R/W = 1) the PLL.

In the data portion of the telegram during a WRITE operation, the first bit of the first or third data byte determines whether a divider ratio or control information is to follow. In each case the second byte of the same data type has to follow the first byte.

If the address byte indicates a READ operation, the PLL generates an acknowledge and then shifts out the status byte onto the SDA line. If the processor generates an acknowledge, a further status byte is output; otherwise the data line is released to allow the processor to generate a stop condition. The status word consists of two bits from the TTL input ports, three bits from the A/D converter, the lock flag and the poweron flag.

Four different chip addresses can be set by appropriate connection of pin CAS (see table 2 "address selection").

When the supply voltage is applied, a power-on reset circuit prevents the PLL from setting the SDA line to LOW, which would block the bus. The power-on reset flag POR is set at power-on and when V<sub>VCCD</sub> goes below 3.2 V. It will be reset at the end of a READ operation.

The lock detector resets the lock flag FL when the width of the charge pump current pulses is greater than the period of the crystal oscillator (i.e. 250 ns). Hence, when FL = 1, the maximum deviation of the input frequency from the programmed frequency is given by

$$\Delta f = \pm I_P (K_{VCO} / f_O) (C_1 + C_2) / (C_1 C_2)$$

where IP is the charge pump current, KVCO the VCO gain, fQ the crystal oscillator frequency and C1, C2 the capacitances in the loop filter (see application circuit). As the charge pump pulses at 62.5 kHz (=  $f_{rof}$ ), it takes a maximum of 16 µs for FL to be reset after the loop has lost lock state.

Once FL has been reset, it is set only if the charge pump pulse width is less than 250 ns for eight consecutive f<sub>ref</sub> periods. Therefore it takes between 128 and 144 µs for FL to be set after the loop regains the lock state.

## SIEMENS Preliminary IC-SPECIFICATION TDA 6060XS, TDA 6060G

#### Table 1: Bit Allocation Read/Write Data

|                      | MSB | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | LSB | Ack |

|----------------------|-----|------|------|------|------|------|------|-----|-----|

| Write Data           |     |      |      |      |      |      |      |     |     |

| Address Byte         | 1   | 1    | 0    | 0    | 0    | MA1  | MA0  | 0   | Ack |

| Prog. Divider Byte1  | 0   | n14  | n13  | n12  | n11  | n10  | n9   | n8  | Ack |

| Prog. Divider Byte 2 | n7  | n6   | n5   | n4   | n3   | n2   | SC1  | SC0 | Ack |

| Control Byte1        | 1   | PN   | AU1  | AU0  | х    | х    | os   | FS  | Ack |

| Control Byte 2       | TP  | VG1  | VG0  | MD1  | MD0  | P2   | PS1  | PS0 | Ack |

| Read Data            |     | i    | i    | :    |      | :    |      |     |     |

| Address Byte         | 1   | 1    | 0    | 0    | 0    | MA1  | MA0  | 1   | Ack |

| Status Byte          | POR | FL   | Х    | FLV  | х    | A2   | A1   | A0  | Ack |

note: MSB is shifted first.

x = don't care

#### Divider ratio:

**TDA 6060XS:** N = 16384 x n14 + 8192 x n13 + 4096 x n12 + 2048 x n11 + 1024 x n10 + 512 x n9 + 256 x n8 +128 x n7 + 64 x n6 + 32 x n5 + 16 x n4 + 8 x n3 + 4 x n2 + **0** + 0

**TDA 6060G:** N = 16384 x n14 + 8192 x n13 + 4096 x n12 + 2048 x n11 + 1024 x n10 + 512 x n9 + 256 x n8 +128 x n7 + 64 x n6 + 32 x n5 + 16 x n4 + 8 x n3 + 4 x n2 + **2** + 0

**MA0/1:** Address selection (table 2)

PN: 1 negative modulation for video and FM for sound carriers (AudinFM active)

0 positive modulation for video and AM modulation for sound carrier (AudinAM active)

AU 0/1: Audio mode bits and Sound / RF VCO off mode (table 4)

SC0/1: Sound carrier bits (table 5)

**OS:** 1 disables V<sub>TUNE</sub> (for external VCO adjustment)

0 normal PLL operation

**FS:** When quartz oscillator is in slave mode:

external frequency is 62.5 kHz, for test and special applications (test pattern and PLL lock in flag FL not available, sound carrier frequencies incorrect)

0 external frequency is 4 MHz

TP:1 1 test pattern generator on

0 normal operation

**VG0/1:** Video gain setting (table 6) **MD0/1:** Modulation depth (table 7)

Port P2: 1 open-collector output is active

0 open-collector output is inactive, ADC available

**PS0/1:** Picture / sound ratio setting (table 8)

**POR:** Power on reset, flag is set at power-on and reset at the end of READ operation

FL: PLL lock indicator, flag is set when loop is locked

FLV: Clipping detector, flag is set when clipping duration is longer than 1μsec

A0/1/2: A/D converter levels when P2 works as input (table 9)

#### **SIEMENS Preliminary IC-SPECIFICATION TDA 6060XS, TDA 6060G**

#### **Table 2: Address Selection**

| Voltage at CAS               | MA1 | MA0 |

|------------------------------|-----|-----|

| (00.1) * V <sub>VCCD</sub>   | 0   | 0   |

| open circuit                 | 0   | 1   |

| (0.40.6) * V <sub>VCCD</sub> | 1   | 0   |

| (0.91) * V <sub>VCCD</sub>   | 1   | 1   |

#### **Table 3: Audio Modes**

| Audio mode                                        | PN | AU1 | AU0 |

|---------------------------------------------------|----|-----|-----|

| Normal audio operation AM                         | 0  | 0   | 0   |

| 5 x I switch for sound PLL                        | 0  | 1   | 0   |

| Sound carrier off                                 | 0  | 0   | 1   |

| RF VCO off (PN bit = 0) positive modulation       | 0  | 1   | 1   |

| Normal audio operation                            | 1  | 0   | 0   |

| Audio level -1dB (PN bit = 1) negative modulation | 1  | 1   | 0   |

| Audio level -2dB (PN bit = 1) negative modulation | 1  | 0   | 1   |

| Audio level -3dB (PN bit = 1) negative modulation | 1  | 1   | 1   |

#### **Table 4: Sound Carrier Frequencies**

| SC Frequency | SC1 | SC0 |

|--------------|-----|-----|

| 4.5 MHz      | 0   | 0   |

| 5.5 MHz      | 0   | 1   |

| 6.0 MHz      | 1   | 0   |

| 6.5 MHz      | 1   | 1   |

#### **SIEMENS Preliminary IC-SPECIFICATION TDA 6060XS, TDA 6060G**

#### **Table 5: Video Gain Setting**

| Video Gain       | VG1 | VG0 |

|------------------|-----|-----|

| Normal operation | 0   | 0   |

| -1 dB            | 0   | 1   |

| -2 dB            | 1   | 0   |

| -3 dB            | 1   | 1   |

#### **Table 6: Modulation Depth Adjustment**

| Modulation Depth | MD1 | MD0 |

|------------------|-----|-----|

| Normal operation | 0   | 0   |

| + 5 %            | 0   | 1   |

| - 5 %            | 1   | 0   |

| -10 %            | 1   | 1   |

#### **Table 7: Picture Carrier / Sound Carrier Adjustment**

| Picture Carrier to Sound Carrier Ratio | PS1 | PS0 |

|----------------------------------------|-----|-----|

| Normal operation                       | 0   | 0   |

| - 1 dB                                 | 0   | 1   |

| +1 dB                                  | 1   | 0   |

| +2 dB                                  | 1   | 1   |

#### Table 8: A / D Converter Levels

| Voltage at P2 / ADC            | A2 | <b>A</b> 1 | A0 |

|--------------------------------|----|------------|----|

| (0.000.15) * V <sub>VCCD</sub> | 0  | 0          | 0  |

| (0.150.30) * V <sub>VCCD</sub> | 0  | 0          | 1  |

| (0.300.45) * V <sub>VCCD</sub> | 0  | 1          | 0  |

| (0.450.60) * V <sub>VCCD</sub> | 0  | 1          | 1  |

| (0.601.00) * V <sub>VCCD</sub> | 1  | 0          | 0  |

#### **Table 9: Test Pin Configuration**

| Picture Carrier to Sound Carrier Ratio        | T2 | T1 |

|-----------------------------------------------|----|----|

| f cy at P2 (P2 working as output; bit P2 = 1) | 0  | 0  |

| fref ar P2 (P2 working as output; bit P2 = 1) | 0  | 1  |

| RF modulator in overmodulation mode           | 1  | 0  |

| Normal operation                              | 1  | 1  |

#### **Telegram examples:**

Start-Addr-DR1-DR2-CW1-CW2-Stop Start-Addr-CW1-CW2-DR1-DR2-Stop Start-Addr-DR1-DR2-Stop Start-Addr-CW1-CW2-Stop Start-Addr-ST-Stop

Start = start condition Addr = address

= divider ratio 1st byte DR1 DR2 = divider ratio 2nd byte = control word 1st byte CW2 = control word 2nd byte SIEMENS

Preliminary IC-SPECIFICATION

6060XS, TDA 6060G

Stop = stop condition ST = read status byte

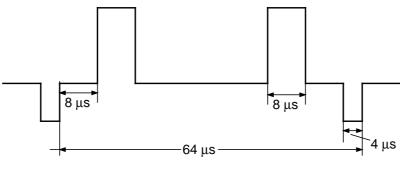

**Test picture**

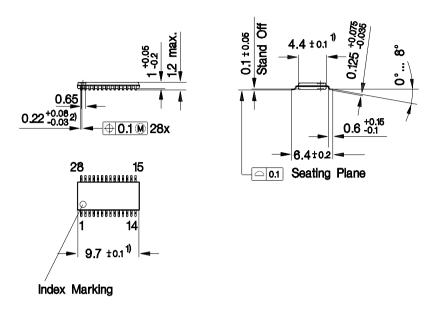

#### Pinning, Package

Plastic Package, P-TSSOP-28-1 (Plastic Thin Shrink Small Outline Package)

- 1) Does not include plastic or metal protrusion of 0.15 max. per side

- 2) Does not include dambar protrusion of 0.08 max. per side

## **Absolute Maximum Ratings**

The maximum ratings may not be exceeded under any circumstances, not even momentarily and individually, as permanent damage to the IC will result.

Ambient temperature  $T_{amb} = 0 \text{ °C...+80 °C}$

| #   | Parameter                                | Symbol Limit Values    |      | /alues            | Units | Remarks        |

|-----|------------------------------------------|------------------------|------|-------------------|-------|----------------|

|     |                                          |                        | Min  | Max               |       |                |

| PLL |                                          |                        |      |                   |       |                |

| 1   | Supply voltage                           | $V_{\sf VCCD}$         | -0.3 | +6                | V     |                |

| 2   | Output CHGPMP                            | $V_{CHGPMP}$           | -0.3 | +3.5              | V     |                |

| 3   | Crystal oscillator pins Q, Qx            | $V_{Q}$                | -0.3 | V <sub>VCCD</sub> | V     |                |

| 4   | Bus input/output SDA                     | $V_{SDA}$              | -0.3 | +6                | V     |                |

| 5   | Bus input SCL                            | $V_{SCL}$              | -0.3 | +6                | V     |                |

| 6   | Chip address switch CAS                  | V <sub>CAUS</sub>      | -0.3 | V <sub>VCCD</sub> | V     |                |

| 7   | Output active filter V <sub>TUNE</sub>   | V <sub>TUNE</sub>      | -0.3 | +35               | V     |                |

| 8   | Bus output SDA                           | I <sub>SDAL</sub>      | 0    | 5                 | mA    | open collector |

| 9   | Port output P2                           | $I_{PL}$               | 0    | 20                | mA    | open collector |

| 10  | Port output P2                           | $V_{P}$                | -0.3 | +6                | V     |                |

| Mod | ulator                                   |                        |      |                   | l     |                |

| 11  | Difference of supply voltages            | V <sub>VCCD</sub> -    | -0.3 | +0.3              | V     |                |

| 12  | Supply voltage                           | $V_{\text{VCCA}}$      | -0.3 | +6                | V     |                |

| 13  | Video Input                              | I <sub>Vidin</sub>     | -0.3 | 3.5               | V     |                |

| 14  | Modulator outputs                        | V <sub>Modout1/2</sub> |      | 6                 | V     | open collector |

| 15  | Modulator outputs                        | V <sub>Modout1/2</sub> | -2   |                   | mA    | open collector |

| 16  | FM Audio Input                           | $V_{\sf AudinFM}$      | -0.3 | +6                | V     |                |

| 17  | AM Audio Input                           | $V_{\sf AudinAM}$      | -0.3 | +6                | V     |                |

| 18  | Second sound carrier input               | V <sub>SC2in</sub>     | -0.3 | +6                | V     |                |

| Gen | eral Items                               | ı                      | ı    |                   | 1     | '              |

| 19  | Junction temperature                     | TJ                     |      | +125              | °C    |                |

| 20  | Storage temperature                      | $T_{S}$                | -40  | +125              | °C    |                |

| 21  | Thermal resistance (junction to ambient) | R <sub>thJA</sub>      |      | 130               | K/W   |                |

| 22  | ESD protection <sup>a</sup>              | $V_{ESD}$              | -1   | +1                | kV    | НВМ            |

a. according to MIL STD 883D, method 3015.7 and EOS/ESD assn. standard S5.1 - 1993

#### **SIEMENS Preliminary IC-SPECIFICATION TDA 6060XS, TDA 6060G**

## **Operational Range**

Within the operational range the IC operates as described in the circuit description. The AC/DC characteristic limits are not guaranteed. Ambient temperature  $T_{\rm amb}$  = 0 °C...+80 °C

| # | Parameter                      | Symbol           | Limit Va | Limit Values |                  | Remarks                         |

|---|--------------------------------|------------------|----------|--------------|------------------|---------------------------------|

|   |                                |                  | Min      | Max          |                  |                                 |

| 1 | Supply voltage                 | $V_{\sf VCCD}$   | +4.5     | +5.5         | V                |                                 |

| 2 | Supply voltage                 | $V_{\sf VCCA}$   | +4.5     | +5.5         | V                |                                 |

| 3 | Programmable divider factor    | N                | 256      | 32764        |                  | by 4, TDA 6060XS                |

| 4 | Programmable divider factor    | N                | 258      | 32766        |                  | by 4, TDA 6060G                 |

| 5 | Video input voltage range      | $V_{Vidin}$      | 0.3      | 1            | V <sub>pp</sub>  | nominal 500mVpp                 |

| 6 | Audio input voltage (FM or AM) | $V_{Audin}$      |          | 1            | V <sub>rms</sub> | nominal 500mVrms,<br>40Hz-15kHz |

| 7 | Oscillator frequency range     | fo               | 30       | 950          | MHz              |                                 |

| 8 | Ambient temperature            | T <sub>amb</sub> | 0        | +80          | °C               |                                 |

#### **AC/DC Characteristics**

AC/DC characteristics involve the spread of values guaranteed within the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

Supply voltage  $V_{VCC} = 5.0 \text{ V}$

**Ambient temperature**  $T_{\rm amb}$  = 25 °C; Ch 21...Ch 69

| #    | Parameter                                              | Symbol                | L            | imit Valı | ues          | Units         | Test Conditions                |

|------|--------------------------------------------------------|-----------------------|--------------|-----------|--------------|---------------|--------------------------------|

|      |                                                        |                       | Min          | Тур       | Max          |               |                                |

| Dig  | ital Part                                              |                       | <del>!</del> | <u> </u>  | <del>'</del> | !             |                                |

| 1    | Supply current                                         | $I_{VCCD}$            | 16           | 21        | 29           | mA            | V <sub>VCCD</sub> = 5 V        |

| PLL  | •                                                      |                       |              |           | '            |               |                                |

| Crys | tal oscillator connections Q,                          | QX                    |              |           |              |               |                                |

| 2    | Crystal frequency                                      | $f_{Q}$               | 3.2          | 4.0       | 4.8          | MHz           | series resonance               |

| 3    | Crystal resistance (1)                                 | $R_{Q}$               | 10           |           | 100          | Ω             | series resonance               |

| 4    | Oscillation frequency                                  | $f_{Q}$               | 3,99975      | 4,000     | 4,00025      | MHz           | $f_{Q} = 4 \text{ MHz}$        |

| 5    | Drive current (1)                                      | $I_{Q}$               |              | 350       |              | $\mu A_{rms}$ | $f_{Q} = 4 \text{ MHz}$        |

| 6    | Input impedance (1)                                    | $Z_{Q}$               | -600         | -750      | -900         | Ω             | $f_{Q} = 4 \text{ MHz}$        |

| 7    | Margin from 1st (fundamental) to 2nd and 3rd harmonics | $a_{H}$               | 20           |           |              | dB            | $f_{Q} = 4 \text{ MHz}$        |

| Cha  | rge pump output CHGPMP (V                              | <sub>VCCD</sub> = 5 V | <u>'</u> )   |           |              |               |                                |

| 8    | Output current                                         | I <sub>CPL</sub>      | ±22          | ±50       | ±75          | μΑ            | <i>V</i> <sub>CP</sub> = 2 V   |

| 9    | Tristate current                                       | I <sub>CPZ</sub>      |              | +1        |              | nA            | OS = 1, V <sub>CP</sub> = 1.3V |

| 10   | Output voltage                                         | $V_{\sf CP}$          | 1.0          |           | 2.5          | V             | locked                         |

| Driv | e output V <sub>TUNE</sub> (open collecto              | or)                   | 1            |           | 1            |               |                                |

| 11   | HIGH output current                                    | I <sub>TH</sub>       |              |           | 10           | μΑ            | V <sub>TH</sub> = 33 V         |

| 12   | LOW output voltage                                     | $V_{TL}$              |              |           | 0.5          | V             | I <sub>TL</sub> = 1.5 mA       |

| Port | output P2 (open collector)                             | •                     | 1            | •         | -            |               |                                |

| 13   | HIGH output current                                    | $I_{POH}$             |              |           | 10           | μΑ            | $V_{POH} = 5V$                 |

| 14   | LOW output voltage                                     | $V_{POL}$             |              |           | 0.5          | V             | $I_{POL}$ = 15 mA              |

| ADC  | port input P2                                          |                       | 1            |           | l            | 1             | 1                              |

| 15   | HIGH input current                                     | $I_{ADCH}$            |              |           | 10           | μΑ            |                                |

| 16   | LOW input current                                      | I <sub>ADCL</sub>     | -10          |           |              | μΑ            |                                |

<sup>(1)</sup> Design note: no 100% final inspection.

#### **AC/DC Characteristics**

AC/DC characteristics involve the spread of values guaranteed within the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

Supply voltage  $V_{VCC} = 5.0 \text{ V}$

$T_{\rm amb}$  = 25 °C; Ch 21...Ch 69 **Ambient temperature**

| #                | Parameter                 | Symbol             |     | Limit Val | ues      | Unit | Test                       |

|------------------|---------------------------|--------------------|-----|-----------|----------|------|----------------------------|

|                  |                           |                    | Min | Тур       | Max      |      | Conditions                 |

| Add              | ress selection input CAS  | •                  |     | •         | •        | •    | •                          |

| 17               | HIGH input current        | I <sub>CASH</sub>  |     |           | 50       | μΑ   | V <sub>CASH</sub> = 5 V    |

| 18               | LOW input current         | I <sub>CASL</sub>  | -50 |           |          | μΑ   | V <sub>CASL</sub> = 0 V    |

| I <sup>2</sup> C | Bus                       |                    | •   | <b>'</b>  | <b>'</b> |      |                            |

|                  | Bus inputs SCL, SDA       |                    |     |           |          |      |                            |

| 19               | HIGH input voltage        | $V_{IH}$           | 3   |           | 5.5      | V    |                            |

| 20               | LOW input voltage         | $V_{IL}$           |     |           | 1.5      | V    |                            |

| 21               | HIGH input current        | I <sub>IH</sub>    |     |           | 10       | μΑ   | $V_{IH} = V_{S}$           |

| 22               | LOW input current         | I <sub>IL</sub>    | -20 |           | 1.0      | μΑ   | $V_{\rm IL} = 0 \text{ V}$ |

|                  | output SDA (open collecte |                    |     |           |          | μπ   |                            |

| 23               | HIGH output current       | I <sub>OH</sub>    |     |           | 10       | μΑ   | V <sub>OH</sub> = 5.5 V    |

| 24               | LOW output voltage        | V <sub>OL</sub>    |     |           | 0.4      | V    | $I_{OL} = 3 \text{ mA}$    |

|                  | e speed SCL,SDA           | , OL               |     |           | 0.4      |      | 101 - 0 11/1               |

| 25               | Rise time                 | $t_{r}$            |     |           | 300      | ns   |                            |

| 26               | Fall time                 |                    |     |           | 300      | ns   | +                          |

|                  | ck timing SCL             | t <sub>f</sub>     |     |           | 300      | 113  |                            |

| 27               | Frequency                 | f                  | 0   |           | 400      | kHz  | 1                          |

| 28               | HIGH pulse width          | f <sub>SCL</sub>   | 0.6 |           | 400      | μς   |                            |

| 29               | LOW pulse width           | t <sub>H</sub>     | 1.3 |           |          | +    |                            |

|                  | t condition               | t <sub>L</sub>     | 1.3 |           |          | μs   |                            |

|                  |                           |                    | 0.0 |           |          | 1    |                            |

| 30               | Set-up time               | t <sub>susta</sub> | 0.6 |           |          | μs   |                            |

| 31               | Hold time                 | <sup>t</sup> hsta  | 0.6 |           |          | μs   |                            |

| Stop             | condition                 |                    |     |           |          |      |                            |

| 32               | Set up time               | t <sub>susto</sub> | 0.6 |           |          | μs   |                            |

| 33               | Bus free                  | t <sub>buf</sub>   | 1.3 |           |          | μs   |                            |

#### **AC/DC Characteristics**

AC/DC characteristics involve the spread of values guaranteed within the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

Supply voltage  $V_{VCC}$  = 5.0 V

**Ambient temperature**  $T_{\rm amb} = 25 \, ^{\circ}\text{C}$ ; Ch 21...Ch 69

| #    | Parameter                                      | Symbol             | Limit Values |     |     | Units           | Test                          |

|------|------------------------------------------------|--------------------|--------------|-----|-----|-----------------|-------------------------------|

|      |                                                |                    | Min          | Тур | Max |                 | Conditions                    |

| Data | transfer                                       |                    |              | •   | •   | •               | •                             |

| 34   | Set-up time                                    | <sup>t</sup> sudat | 0.1          |     |     | μs              |                               |

| 35   | Hold time                                      | <sup>t</sup> hdat  | 0            |     |     | μs              |                               |

| 36   | Input hysteresis<br>SCL, SDA <sup>(1)</sup>    | $V_{hys}$          |              | 200 |     | mV              |                               |

| 37   | Noise immunity<br>SCL, SDA <sup>(1), (2)</sup> | $V_{N}$            |              | 5   |     | V <sub>pp</sub> | $f_{N} = 2 \text{ MHz14 MHz}$ |

| 38   | Capacitive load for each bus line              | $C_{L}$            |              |     | 400 | pF              |                               |

<sup>(1)</sup> Design note: no 100% final inspection (2) Sinusoidal noise signal applied via a 33 pF coupling capacitor

#### **Analog Part**

| 39   | Supply current                               | I <sub>VCCA</sub>                     | 33       | 43       | 57       | mA              | incl. mixer outputs                                                                                             |

|------|----------------------------------------------|---------------------------------------|----------|----------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------|

| Vide | o modulator                                  |                                       |          | •        | •        | •               | •                                                                                                               |

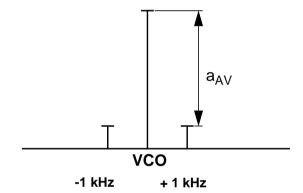

| 40   | Video input voltage                          | $V_{Vidin}$                           |          | 0.5      |          | V <sub>pp</sub> |                                                                                                                 |

| 41   | Video gain steps                             | Δ Gain                                |          | -3       |          | dB              | 3 steps, 1 dB each                                                                                              |

| 42   | Step width of gain setting                   | δ Gain                                | 0.8      | 1        | 1.2      | dB              |                                                                                                                 |

| 43   | Intermodulation ratio                        | $a_{IMA}$                             | 60       |          |          | dB              | f <sub>SC</sub> - f <sub>CC</sub>                                                                               |

| 44   | Harmonic wave ratio                          | $a_{H}$                               | 60       |          |          | dB              | f <sub>PC</sub> +2f <sub>CC</sub> ;<br>f <sub>PC</sub> +3f <sub>CC</sub> ;<br>f <sub>PC</sub> +4f <sub>CC</sub> |

| 45   | Modulation depth                             | $m_{\mathrm{D/N}} \ m_{\mathrm{D/P}}$ | 80<br>80 | 90<br>90 | 98<br>98 | %<br>%          |                                                                                                                 |

| 46   | Modulation depth adj. range                  | $\Delta m_{D}$                        | -10      |          | +5       | %               |                                                                                                                 |

| 47   | Video signal to noise ratio<br>Ch21 or lower | V <sub>S+N/N</sub>                    | 48       | 51       |          | dB              | CCIR 17-line bar, line 22                                                                                       |

| 48   | Video signal to noise ratio<br>Ch69          | V <sub>S+N/N</sub>                    | 45       | 48       |          | dB              | HP =200kHz<br>LP = 5MHz<br>unweighted                                                                           |

| 49   | Audio in Video<br>(*test procedure1)         | $a_{AV}$                              | 54       | 60       |          | dB              | FM modulation;<br>$\Delta f = 27 \text{kHz}$ ;<br>$V_{\text{Vidin}} = 0 \text{ V}_{\text{pp}}$                  |

#### **AC/DC Characteristics**

AC/DC characteristics involve the spread of values guaranteed within the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

Supply voltage

$V_{\text{VCC}} = 5.0 \text{ V}$

**Ambient temperature**

$T_{\rm amb} = 25 \, ^{\circ}\text{C}$ ; Ch 21...Ch 69

| #    | Parameter                            | Symbol                   |      | Limit Val | ues            | Units             | Test<br>Conditions                                                                         |

|------|--------------------------------------|--------------------------|------|-----------|----------------|-------------------|--------------------------------------------------------------------------------------------|

|      |                                      |                          | Min  | Тур       | Max            |                   |                                                                                            |

| Vide | o modulator                          |                          |      |           |                |                   | 1                                                                                          |

| 49   | Audio in Video<br>(*test procedure1) | $a_{AV}$                 | 54   | 60        |                | dB                | AM modulation;<br>m = 65 %;<br>$V_{Vidin} = 0 V_{pp}$                                      |

| 50   | Differential gain                    | DG                       |      | 3         | 5              | %                 | $V_{\text{Vidin}} = 0.5 \text{ V}_{\text{pp}}$                                             |

| 51   | Differential phase                   | DP                       |      | 1         | 5              | deg               | $V_{\text{Vidin}} = 0.5 \text{ V}_{\text{pp}}$                                             |

| 52   | Video frequency response             | $a_{V}$                  |      |           | ±1             | dB                | f = 50 Hz5 MHz                                                                             |

| FM ı | nodulator                            | •                        | •    | '         | <u>'</u>       | •                 | -                                                                                          |

| 53   | FM audio input voltage*              | $V_{Audin^*}$            |      | 0.5       |                | V <sub>rms</sub>  | * At pre-emphasis network input                                                            |

| 54   | FM carrier frequency range           | FM <sub>C</sub>          | 4.5  |           | 6.5            | MHz               |                                                                                            |

|      | FM deviation                         |                          |      |           |                |                   | $V_{\text{Audin* rms}} = 0.5 \text{ V};$<br>$f_{\text{AF}} = 1 \text{ kHz}$                |

| 55   | SC = 6.5 MHz                         | ΔFM                      | 28   | 35        | 42             | kHz               |                                                                                            |

| 56   | SC = 6.0 MHz                         | $\Delta$ FM              | 24   | 30        | 36             | kHz               |                                                                                            |

| 57   | SC = 5.5 MHz                         | $\Delta$ FM              | 24   | 30        | 36             | kHz               |                                                                                            |

| 58   | SC = 4.5 MHz                         | $\Delta$ FM              | 17.5 | 22        | 26.5           | kHz               |                                                                                            |

| 59   | FM modulation distortion             | <i>THD</i> <sub>FM</sub> |      | 0.3       | 1.5            | %                 | $V_{\text{Audin* rms}} = 0.5 \text{ V}$                                                    |

| 60   | FM signal to noise ratio             | S+N/N                    | 50   | 56        |                | dB                | $f_{\rm AF}$ = 1kHz; $\Delta f$ =50kHz<br>Video: colorbar<br>Ch21,CCIR 468-3<br>quasi peak |

| Sec  | ond Sound Carrier input              | 1                        |      | - 1       |                | 1                 | -                                                                                          |

| 61   | Input DC voltage                     | V <sub>SC2in</sub>       | -0.3 | 0         | +0.3           | V                 | Normal operation                                                                           |

| 62   | Input DC voltage                     | V <sub>SC2in</sub>       | 2    |           | $V_{\sf VCCA}$ | V                 | SC2in OFF                                                                                  |

| 63   | Input AC voltage                     | V <sub>SC2in</sub>       | 30   | 50        | 80             | mV <sub>rms</sub> | FM, SC1: 5.5MHz                                                                            |

| AM   | modulator                            | 1                        | -    |           |                |                   | 1                                                                                          |

| 64   | AM audio input voltage*              | $V_{Audin^*}$            |      | 0.5       |                | V <sub>rms</sub>  | * At voltage divider input                                                                 |

| 65   | AM carrier frequency                 | AM <sub>C</sub>          |      | 6.5       |                | MHz               |                                                                                            |

| 66   | AM modulation factor                 | $m_{AM}$                 | 55   | 60        | 65             | %                 | $V_{\text{Audin* rms}} = 0.5 \text{ V}$                                                    |

#### **AC/DC Characteristics**

AC/DC characteristics involve the spread of values guaranteed within the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

Supply voltage  $V_{\rm VCC}$  = 5.0 V

$T_{\text{amb}} = 25 \,^{\circ}\text{C}$ ; Ch 21...Ch 69 **Ambient temperature**

| #    | Parameter                              | Symbol                                |     | Limit Val | lues | Units    | Test                                                               |

|------|----------------------------------------|---------------------------------------|-----|-----------|------|----------|--------------------------------------------------------------------|

|      |                                        |                                       | Min | Тур       | Max  |          | Conditions                                                         |

| 67   | AM modulation distortion               | <i>THD</i> <sub>AM</sub>              |     |           | 1.5  | %        | $V_{\text{Audin* rms}} = 0.5 \text{ V}$                            |

| 68   | AM signal to noise ratio               | S+N/N                                 | 47  | 50        |      | dB       | $f_{AF}$ = 1 kHz;<br>m = 60%;<br>RMS; CCIR 468;<br>video: colorbar |

| RF N | Modulator, referred to Applica         | tion Board                            | İ   | •         |      |          |                                                                    |

| 69   | Modulator output impedance             | $R_{	ext{Modout}}$ $C_{	ext{Modout}}$ |     | 20<br>0.5 |      | kΩ<br>pF |                                                                    |

| 70   | RF output voltage                      | $V_{Modout}$                          | 77  | 80        |      | dBμV     | RL = 75 Ω                                                          |

| 71   | RF output harmonics (n = 2)            | a <sub>RF2</sub>                      |     | -15       | -10  | dBc      | $f_{\text{Modout}} = 470 \text{ to } 860$ MHz                      |

| 72   | Picture Sound carrier ratio TDA 6060XS | PC / SC ratio                         | 8   | 11        | 14   | dB       | L; M; DK standard<br>f=4.5MHz, 6.5MHz                              |

| 73   | Picture Sound carrier ratio TDA 6060XS | PC / SC ratio                         | 10  | 13        | 16   | dB       | B/G; I standard<br>f=5.5MHz, 6.0MHz                                |

| 74   | Picture Sound carrier ratio TDA 6060G  | PC / SC ratio                         | 11  | 14        | 17   | dB       | L; M; DK standard<br>f=4.5MHz, 6.5MHz                              |

| 75   | Picture Sound carrier ratio TDA 6060G  | PC / SC ratio                         | 13  | 16        | 19   | dB       | B/G; I standard<br>f=5.5MHz, 6.0MHz                                |

| 76   | Sound carrier harmonics                | THD SC                                | 55  | 65        |      | dB       | referenced to picture carrier                                      |

| 77   | Rejection of PLL refence frequency     | a fref                                | 60  |           |      | dB       |                                                                    |

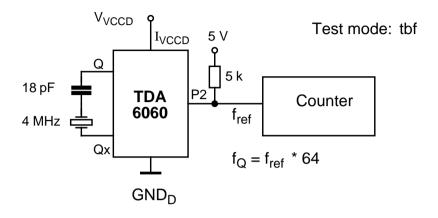

## **Test Circuit 1**

## **Measurement of Crystal Oscillator Frequency**

#### Test Procedure 1: Crosstalk Audio in Video

## **Equivalent I/O-Schematic**

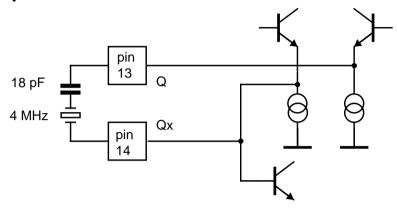

## **Equivalent I/O-Schematic of Quartz Oscillator**

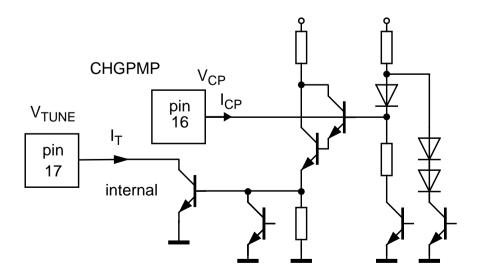

## **Equivalent I/O-Schematic of Charge Pump**

## **Equivalent I/O-Schematic**

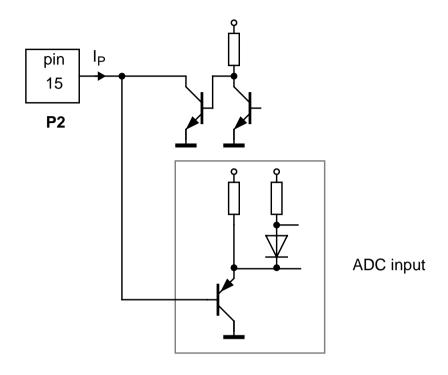

#### **Equivalent I/O-Schematic of Port Pin**

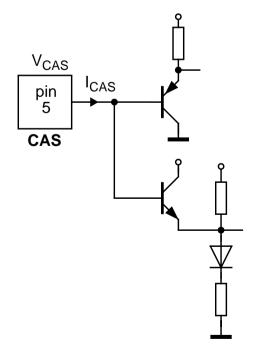

#### **Equivalent I/O-Schematic of CAS Pin**

## **Equivalent I/O-Schematic**

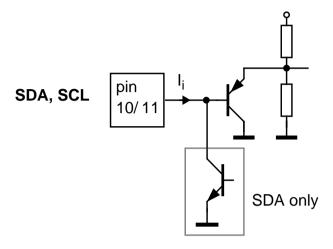

#### **Equivalent I/O-Schematic of SDA/SCL Pins**

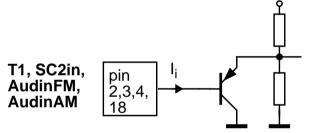

#### Equivalent I/O-Schematic of Pins T1, AudinFM, AudinAM, SC2in

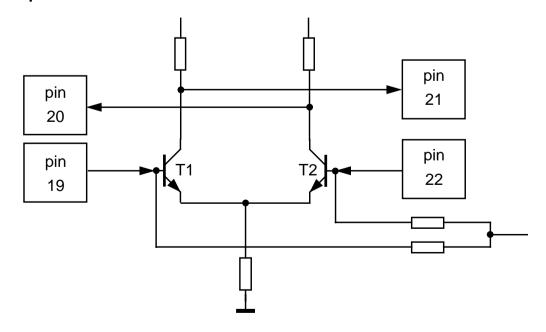

## Equivalent I/O-Schematic of UHF- VHF-Oscillator Pins

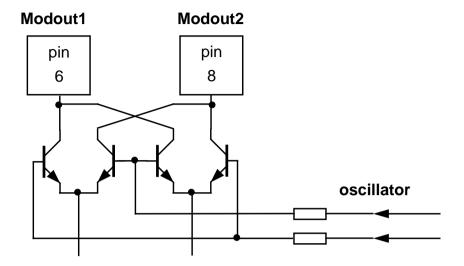

#### **Equivalent I/O-Schematic of Modulator Output Pins**

#### **Equivalent I/O-Schematic of Video Input**

#### Equivalent I/O-Schematic of Filter Pins SLF, TFLF

## **Equivalent I/O-Schematic of Filter Pin T2**

SIEMENS

t<sub>buf</sub>  $t_r$  $t_f$ t<sub>susta</sub> t<sub>hsta</sub> tL  $t_{H}^{-}$ t<sub>sudat</sub> t<sub>hdat</sub> t<sub>susto</sub> bus free time data/clock rise time data/clock fall time start set-up time start hold time LOW clock pulse width HIGH clock pulse width data transfer set-up time data transfer hold time stop set-up time

## **Test Circuit Diagram**

## **Application Board**